지난시간에 이어서 오늘은 수식유도를 수학적으로

유도하는 과정을 한번 진행해보도록 합시다.

X4라는 스위치가 열린상태로 있다가.

외부의 힘을 받아서.

탁 닫혔을때, 과연 어떤 형태로 그래프가 그려질까?

우리가 궁금한건.

인덕터 전류 I가 시간에 따라서 어떻게 변화하느냐 입니다.

우리는 이번엔. 지난시간과 다르게 수식유도를 진행할 예정입니다.

이유는. 미분방정식이라는게 굉장히 복잡하기 때문입니다.

그래서 우리는 경험에 근거한 추측성 사실을 바탕으로 결과를 미리 예측하고

그런 추측성 사실이 진짜인지 아닌지를 검증할 겁니다.

지난시간(RC 회로의 미분방정식 풀이 포스팅)엔

키르히호프 법칙을 사용하여 폐회로의 회로상태를 유도하였죠.

근데. 우리는

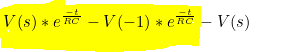

지난 RC회로의 미분방정식 풀이 포스팅에서

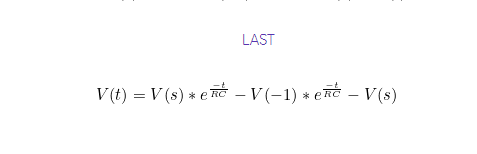

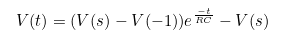

아래와 같은 결론을 얻었습니다.

RL회로도 RC회로와 같이 소자만 바뀌었을뿐이지

실제론 L이나 C나 그 수식이 비슷할거라 추측할수 있는데요.

그렇다면 문제가 더 쉽게 풀리지 않을까?

생각해볼 수 있죠.

수학적인 테크닉을 가지고 말이죠.

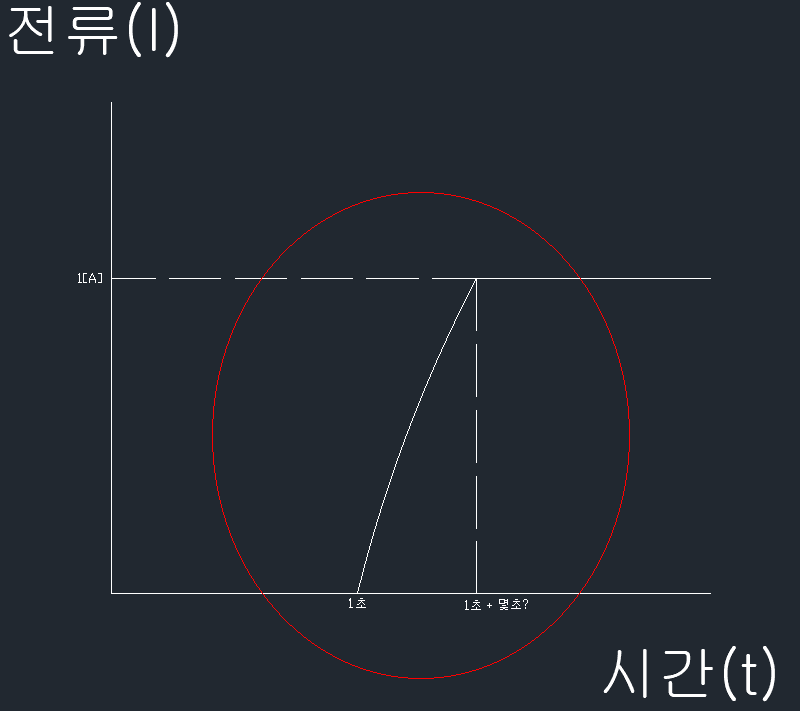

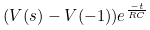

위 수식을 잘 나눠보면

자연로그 e에 관련된 지수함수로

응답이

나타나는 1부분과

시간과 관련없이 전압원에서 정전압을 출력하는

V(s)로 나뉜다는 사실을 알 수 있죠.

즉,

RC 회로의 시간에 따른 전압은

시간에 따라 변화하는 1부분

시간에 따라 변화하지 않는 2부분

으로 나뉜다는 사실을 알 수 있습니다.

여기에서.

1부분은 자연응답 = 과도응답 이라고도함.

2부분은 강제응답 = 정상응답 이라고도함.

이라고 명칭되어 사용 됩니다.

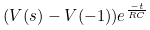

그림에서 보면 바로

곡선구간이 나타나는 저부분이

이 성분인거고.

그리고 직선구간이 나타나는 저부분이

이 성분인거죠.

우리는 RL 회로의 미분방정식 풀이를 하지 않았지만.

RL 회로도 RC회로와 비슷한 .

에너지 저장 소자라는 사실을 알고 있으며,

이로 미루어보면 분명 RL회로도 지수함수 형태의 그래프를 띈다고

추측할 수 있습니다.

우선은 지수함수 형태의 그래프를 띄는지 안띄는지는 수식을 유도하고

차후 검증하면 되는것이고.

우선은 지수함수로써

인덕터 전류 I 가 어떻게 변화하는지 알아보도록 하죠.

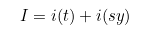

우린 인덕터 전류가 궁금하다 하였었죠.

인덕터 전류는 수식유도는 잘모르겠고

우선은 결론을 먼저 짓고 시작할게요.

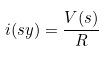

이 수식도 자세히보면,

시간에 따라 전류가 변화하는 i(t) 부분과

시간에 따라 전류가 변화하지 않는 i(steady) = i(sy) 부분으로

나뉜다는 걸 미리 결론으로 깔고 들어가자는 겁니다.

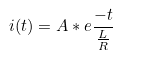

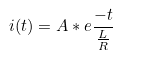

그리고 RC회로를 유도하면서 우리는 경험치를 높일 수 있었습니다.

과도응답은. 지수함수 형태로 감쇄한다는 사실을 알았죠.

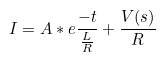

그래서 우리는 아래 사실을 도출할 수 있습니다.

i(t)가 어떻게 생겨먹었는진 모르겠는데

일단 이렇게 정의할 순 있겠다.

고 생각하고 문제를 접근하는 겁니다.

아니 A는 뭐고 지수함수에 저딴 형태는 어떻게

알 수 있는거냐고 따질 수 있겠죠?

그야 과거에도 그랬으니까.

이번에도 추측할 수 있는 것(맞는지 틀린진 모름)이죠.

과도상태라는 것이 자연로그 함수로 표현되며

제곱 부분에 시간축은 -형태로 존재한다는 사실도 알고.

다만, RC와 RL과 다른부분은 시정수인

RC, L/R 부분인건데.

이거는 사실. 키르히호프 법칙을 실제 유도했을때나

확인할 수 있는 부분이긴 합니다.,

어쨋든. 결론을 먼저 지어놓고 역으로 맞는지 검증하기로 했으니까.

한번보죠.

지금 우선 과도응답 부분은 정리가 됬군요.,

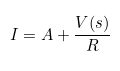

정상응답은 쉽습니다.

회로를 보면 전압원 V(s)가.

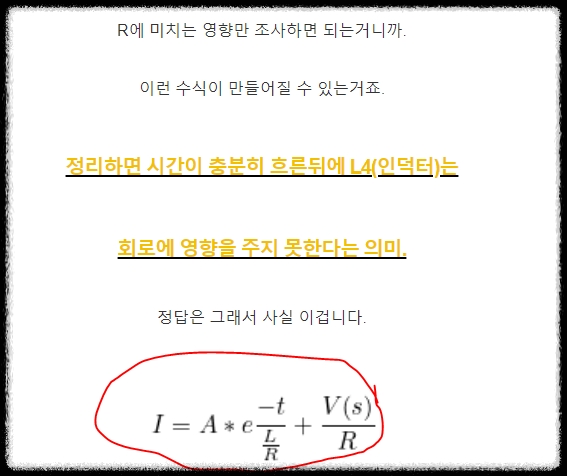

R에 미치는 영향만 조사하면 되는거니까.

이런 수식이 만들어질 수 있는거죠.

정리하면 시간이 충분히 흐른뒤에 L4(인덕터)는

회로에 영향을 주지 못한다는 의미.

정답은 그래서 사실 이겁니다.

A를 구하기 위해서는

t = 0을 대입했을때 상황을 따져보면됩니다.

t가 0이되면, R이나 L값에 상관없이

자연로그 함수는 1이 될 것이고요.

수식은 이렇게 정리될 겁니다.

V(s)는 전압원이니까 상수

R도 상수

I = 초기에 인덕터에 흐르는 전류

가 되겠죠.

자. 사실 이 수식유도는

완전 개판 엉망입니다.

저는 대학생때 이러한 수식유도가 너무 화가났습니다.

결론을 알고서 답을 내리면 이건 논리 비약을 넘어서

호기심 가득한 학생의

배움을 우롱하는 행위 아닌가?

지금 생각해보면 이런 논리적인 비약이 너무자주. 매우많이 일어나서

안그래도 어려운 전기공학을 더 어렵게 느껴

모든 수식과 논리를 이해없이 중간, 기말을 잘보기위해 단순 암기만 했었다는

사실이 화가납니다.

사실 이러한 수식을 보고 이렇게까지 생각하는 사람은

저뿐이었는지도 모르겠습니다.

엔지니어는 창의적으로 생각할 수 있어야 합니다.

사실 저는 물류자동화 설계엔지니어로 약 6년간 일하면서

느끼건데.

지금 배우고있는

이런 수식유도 따위는 중요하지 않습니다.

누군가 훌륭한 툴을 이미 만들어놨고 난 그걸 몇번의 마우스

클릭으로 해결할 수 있는 틀이 이미 갖춰졌거든요.

그런데. 그러한 엔지니어들도

어떠한 문제를 해결하는 과정에서는 적당한 논리가 필요합니다.

논리라는 것은 기초에 근거해 쌓일 수 있는것이라 믿습니다.

헌데 대학의 교과서가

이런식으로 써져있는게 저는 너무 화가났습니다.

기초가 아니라. 그냥 책에 똑같은 수식유도 하기 귀찮아서 대충 넘어가는 걸로

보였달까요?

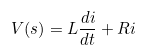

어쨋든. 저는 여러분이 배웠던 키르히호프 법칙 고대로 써서 수식

유도해보겠습니다.

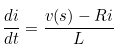

위 수식에 키르히호프 법칙을 적용하면

아래와 같이 수식을 유도할 수 있습니다,

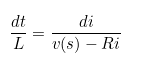

이 수식을 이렇게 표현해볼까요?

다시한번 정리해보겠습니다.

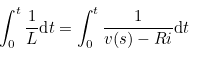

양변을 시간으로 적분해보겠습니다

di라고 써져있는

적분인자 역시. 시간에 따른 변수임을 상기하면서

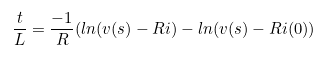

다시 정리하면.

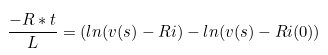

또한 번 정리하면...

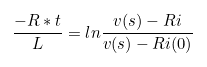

ln의 차는 수식 나눗셈으로 표현될 수 있죠?(공학수학 참고)

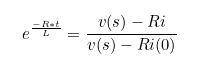

이 수식에서 양변에 e인 자연로그를 취해봅시다.

그럼 결과는.

이수식 어디서 많이 보지 않았나 싶네요.

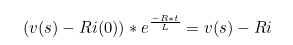

일단 분모를 삭제해봅시다.

여기서 수식을 i에 대해서 정리하면.

우리가 처음에 정리했던 수식과 동일한 수식이 되는겁니다.

사실 제가

수학을 그닥 잘하는 편도 아니고.

공부한지도 너무 오래되서.

수식정리는 애를 참많이 먹네요

이로써.

모든 회로이론의 포스팅을 마무리 하겠습니다.

원래는 조금더 회로이론 관련 포스티을 진행할까 했는데.

이제 전공 초기 과목을 마치고. 상위 과목으로 넘어가도 될 듯 합니다.

지금까지의 긴 공부 여정에 따라와주셔서 감사합니다.

아직 확실히 커리가 정해지지 않았지만

다음에는

제어공학이나 전기기기를

포스팅으로 소개할 예정입니다.

'전기공학 기초이론 > 회로이론' 카테고리의 다른 글

| [회로이론] - RL회로의 계단응답 개요 (0) | 2023.04.23 |

|---|---|

| [회로이론] - RC 회로의 계단응답 시정수(자동차의 제로백) (2) | 2023.04.09 |

| [회로이론] - RC 회로의 계단응답 (보통은 여기서부터 학생들이 포기합니다...) (0) | 2023.04.02 |

| [회로이론] - RL 미분방정식 풀이 ???? 그게 뭔데, 무전원 RL 회로를 알아보자 (0) | 2023.03.26 |

| [회로이론] 전원없이 저항과 커패시터를 연결하면 어떻게 될까? (1) | 2023.03.19 |