지난시간에 이어서

테브난의 예제에 대해서 살펴보는 시간을

가져보고 짧게 끝내보겠습니다.

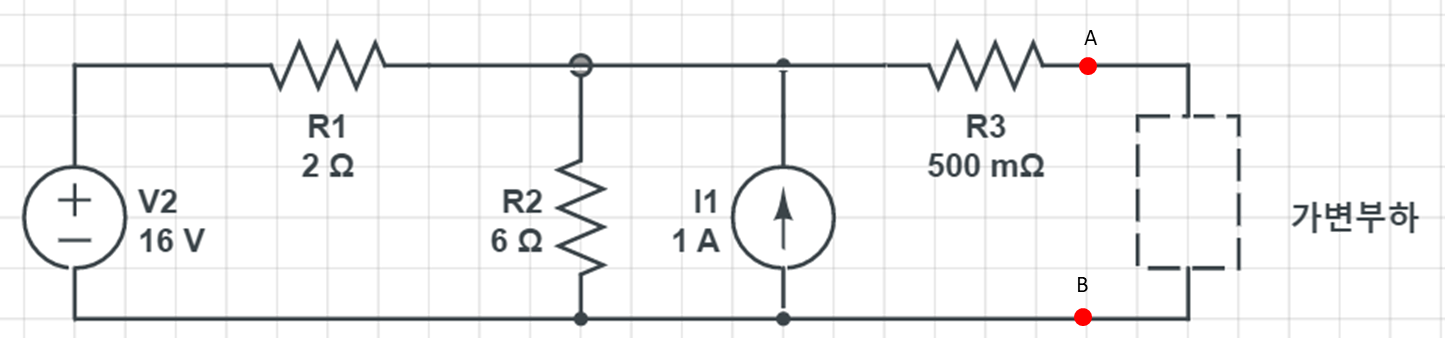

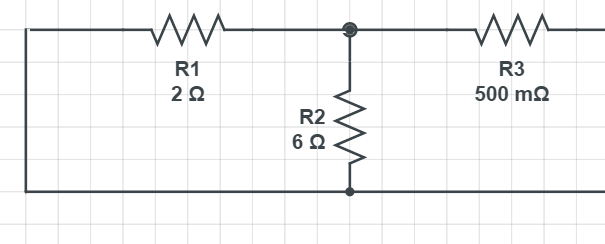

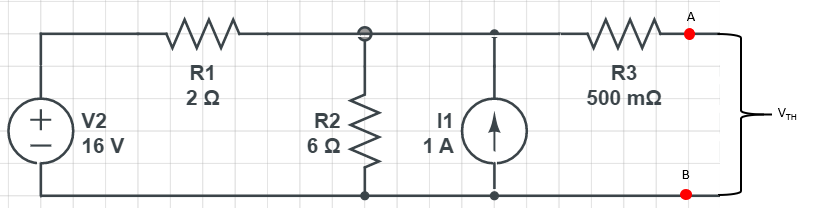

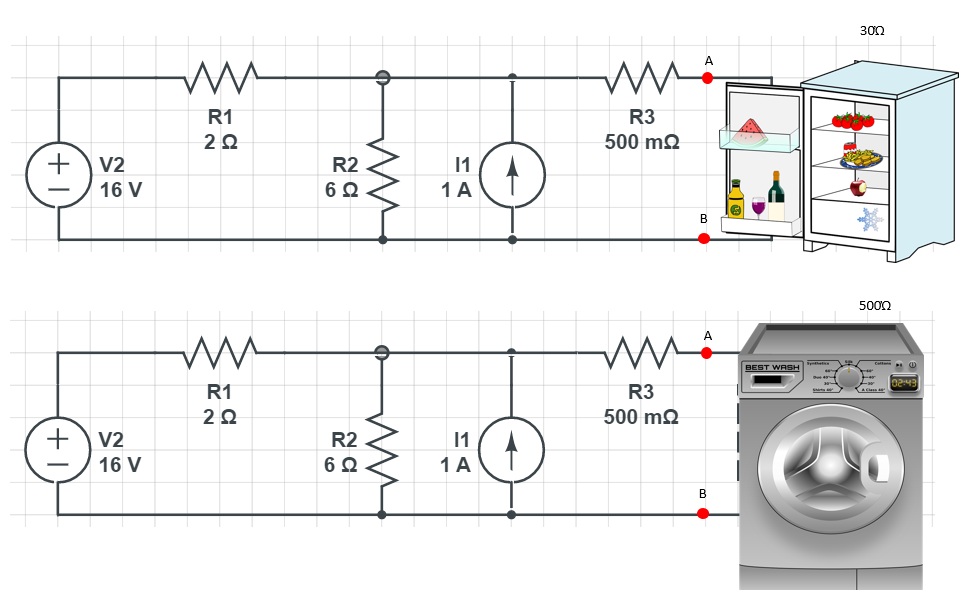

문제는 이렇습니다.

QUEST NO. 1

A, B단자 기준으로

왼쪽의 테브난 등가회로를 구해봅시다.

지난시간에 말씀드렸다시피 2가지

규칙이 있었죠?

기억 안나시는분은 지난번 포스팅 다시 참고해보시길...

아참.

이회로를 들어가기전에 먼저 따져야 하는게 있었죠?

선형성을 만족하느냐에요.

보시다시피 이상적인 전압원, 전류원

저항으로만 이루어진 위 두 회로는 모두 선형성을 만족합니다.

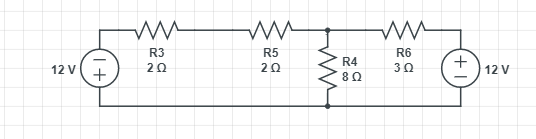

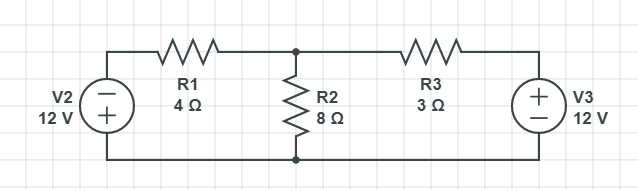

여기서 두회로란...

이상, 2가지 회로를 뜻하는데

두회로는 모두 선형성을 만족한다는 사실을 쉽게 알 수 있을겁니다.

테브난 등가회로가 선형성을 가지는 두회로가 하나의 회로로 변환된다는 사실을

알았을 경우

위 회로는 테브난 등가회로로 변환 가능함을 암시하는데..

이제...

본격적으로 문제를 해결해봅시다.

먼저

테브난 등가저항을 먼저 구해보겠습니다.

테브난 등가저항을 구할때는 먼저...

이상적인 독립전원을 끄라고 말씀드렸었죠?

끄라는 것의 의미는

이상적인 전압원은 단락시켜버리고

이상적인 전류원은 개방시켜버리는 것을

의미합니다.

외우지 마시고 잘 생각해보시면 압니다.

위 회로에서 끄다의 본질적의 의미는 아마도...

'회로 구실을 못하게 만들어버려라' 일 것입니다

전압원이 회로구실을 못하게 만들려면 전압원 양단을

디지털멀티미터로 측정하였을때 0[V] 가 찍혀야겠죠?

이는. 바꾸어 말하면

단락회로와 동일합니다

전류원이 회로구실을 못하게 만들려면 전류원 양단을

디지털멀티미터로 측정하였을때 0[A] 가 찍혀야겠죠?

이는. 바꾸어 말하면

개방회로와 동일하죠.

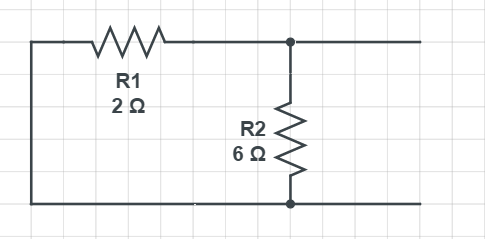

이렇게 두회로의 전압원과 전류원을 끄게되면

아래와 같은 회로가 만들어집니다.

위 회로에서 등가 저항을 구하는 방법은

우리가 이전포스팅에서 배웠던 합성저항 공식과 동일합니다.

먼저 R1과 R2는 병렬회로이므로

1 / (1/2 + 1/6) = R1과 R2의 합성저항

즉,

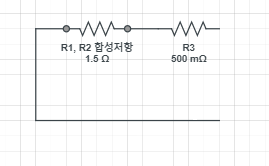

R1과 R2의 합성저항이 1.5 [OHM]

나온다는 사실을 쉽게 구할 수 있고,

마찬가지로 R1 R2의 합성저항 1.5 [OHM]과 R3 0.5 [OHM]이

직렬연결 되어있으므로

R1 R2 R3의 총합성저항이 2 [OHM]이 된다는 사실을 알 수 있습니다.

즉 테브난 등가저항은 2 [OHM] 입니다.

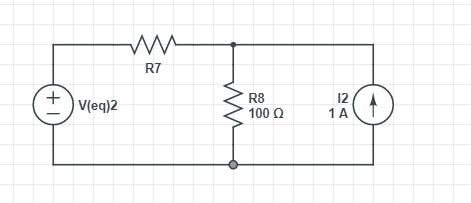

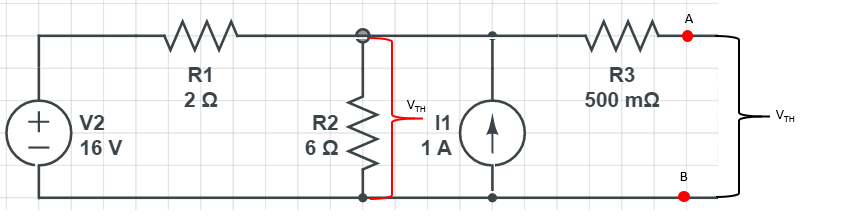

그렇담 테브난 등가 전압은 어떻게 구해야 할까요???

먼저...

테브난 등가전압이라 함은

가변부하단을 제외한 A, B 단자의 왼쪽 회로 전압을 측정한 것이죠.

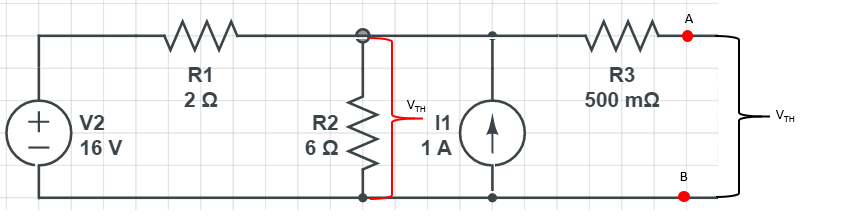

위회로가 이상적인 소자 및 전원만 사용한다고 가정하면 회로 A는

아래 회로 B처럼 대체될 수 있습니다.

그 이유인 즉슨

이상적인 전류원은 저항이 엄청나게 크기 때문에

실상 개방회로와 같기 때문이죠.

여기서 V(th)를 구하는건 식은죽 먹기입니다.

왜냐면...

이미 앞선 포스팅에서 수많은 강의를 해왔기 때문.

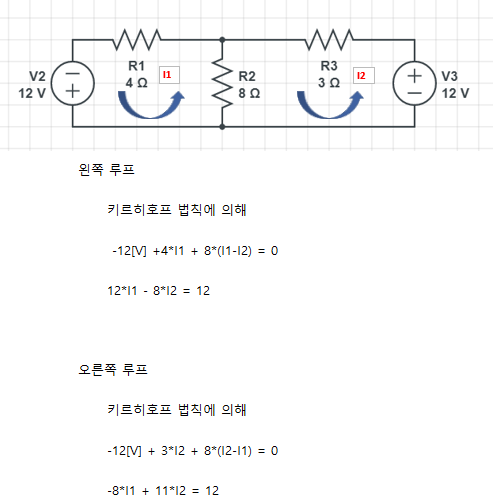

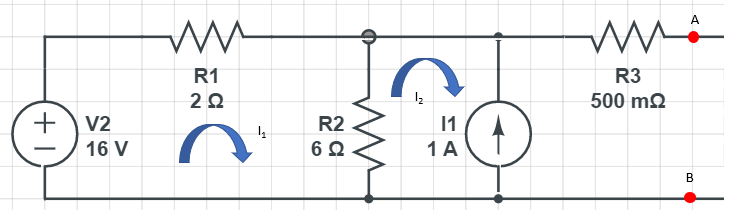

회로B의 각각 루프에 메시를 돌려봅시다.

먼저

-16 + 2 * I1 +6 * (I1 - I2) = 0 ∙∙∙∙ 1번 수식

1번수식을 정리해보면.

8 * I1 - 6 * I2 = 16

I2 = -1[A] ∙∙∙∙ 2번수식

식을 정리해보면

I1 = 1.25[A] 임을 알 수 있음.

즉

Vth는

6* ( 1.25 + 1 ) = 13.5[V]

라는 사실.

정리하면

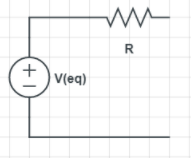

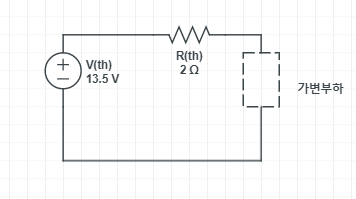

테브난 등가회로는

이렇게 구한 테브난 등가회로는 이렇게 쓰입니다.

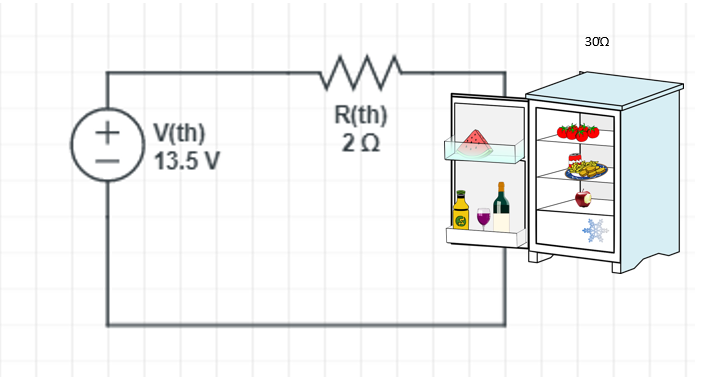

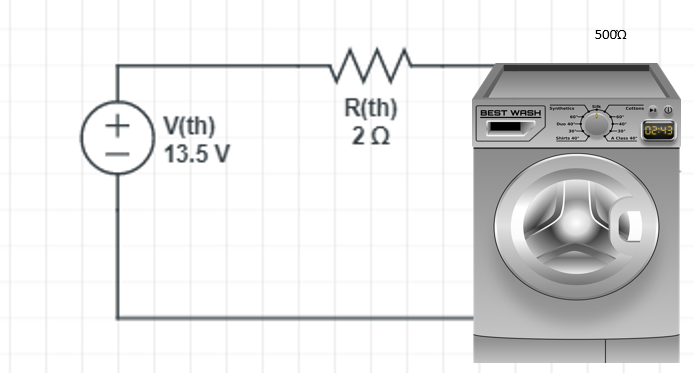

실제로 가변부하는

냉장고가 될 수도 있고

세탁기가 될 수도 있겠죠.

테브난 등가회로로 나타냈으니 망정이지

이거를 이렇게 나타낸다면 얼마나 힘들겠어요???

부하가 바뀔때마다 매번 새로운 회로를 해석해야 하니 말입니다.

무슨이야긴지 충분히 이해하셨으리라 봅니다.

오늘 정신이 없는 상태에서 급하게 포스팅하다보니

계산실수가 있는가 모르겠네요..

무튼 언제든지 문제에 대한 피드백은 환영입니다.

오늘은 여기까지 할게요.

'전기공학 기초이론 > 회로이론' 카테고리의 다른 글

| [회로이론] - 연산증폭기 OP AMP란 무엇인가? - 개요1 (0) | 2022.01.04 |

|---|---|

| [회로이론] - 노턴의 정리 (0) | 2021.12.27 |

| [회로이론] - 테브난 정리 (0) | 2021.12.06 |

| [회로이론] - 전원을 변환해서 회로를 해석할 수 있다고? (0) | 2021.07.18 |

| [회로이론] - 중첩의 원리 (0) | 2021.07.10 |