보통 대학생때 전기공학이건 전자공학이건

전기분야에 몸담는 공학도라면

OP AMP(연산증폭기)에 대해서 한번쯤 들어보신적 있을 겁니다.

제경우 약 10여년전 학부생 당시 연산증폭기가 굉장히 중요하다고

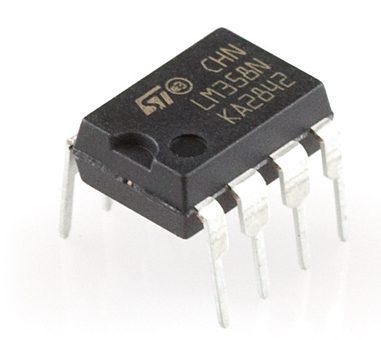

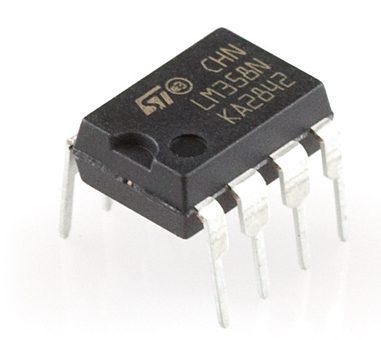

연산증폭기의 실제모습 이미지 출처 https://lampatronics.com/shop/semiconductors/operational-amplifier/lm358-op-amp/

연산증폭기의 실제모습 이미지 출처 https://lampatronics.com/shop/semiconductors/operational-amplifier/lm358-op-amp/

교수님께서 강조하셨던것이 기억에 남네요.

학부생때에는 솔직히 이해따위 필요없고

일단 중간 기말고사는 잘봐야되니까 무작정 머리에 때려넣었습니다.

이해하기에는 늘 공부할 시간이 너무없었고 나가서 술먹고 놀기 바빳거든요.

사실 현업에 종사하는 지금도 저는 OP AMP의 내부 구조에 대해서 자세히 들여다 본적도 없고

100% 이해하지 못하며 100% 이해할 마음도 없습니다.

(원리를 이해하면 물론 좋겠지만, 엔지니어는 누군가가 만들어 놓은 물건을 잘활용하는 능력이

세세한 원리를 이해하는 능력보다 중요함.)

어찌되었건 누군가 만들어 놓은거 잘사용하기만 하면 되는거 아니겠습니까?

저는 어쨋든 여러분들께 제가 학생이었을때 이해가 안가서

그냥 외워야만 했었던 부분을 지금에선 어떻게 이해하게 되었는지와...

그래서 이물건을 어떻게 써먹는다는 건지를 설명하는 부분에 초점을 맞추겠습니다.

이론적인 부분이야 저보다 교과서가 훨씬 자세하게 소개되어 있을테니까요.

그럼 시작하겠습니다.

연산증폭기는 어떻게 탄생했을까요?

때는. 2차세계 대전 이후.

미국 국방부 연구센터에서는 아날로그 컴퓨터를 설계하기 시작하였는데.

컴퓨터라는 장비가 연산과정에 탁월하다는 것은 모두들 아시죠?

컴퓨터 초기 모델을 만들기 위해 개발된 부품으로서

1947년 존 라가지니와 그동료에 의해

소개되었죠.

이러한 연산증폭기의 기능은

간단합니다.

덧셈이나 뺄셈 곱셈이나 나눗셈 심지어 미분적분까지

다양한 수학연산을 가능케합니다.

대단하지 않나요?

사람은 훌륭한 지능체이지만

많은 실수를 범합니다.

그중 가장 많이 저지르는 실수가 바로 계산실수 입니다.

그런 문제를 사라지게 도와준 엄청나게 획기적인 발명이다 이거죠.

정확한데 계산속도도 빠르다면 안사용할 이유가 있을까요?

아시다시피

계산속도로는 인간이 컴퓨터를 앞지를 수 없습니다.

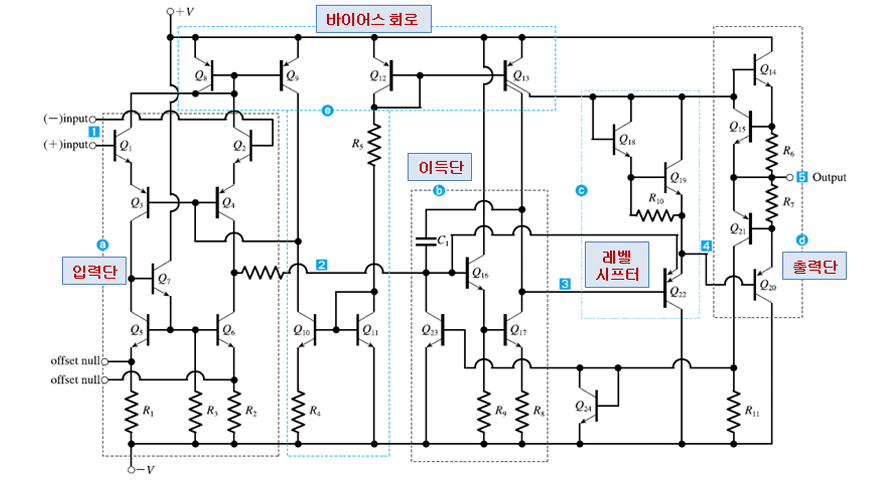

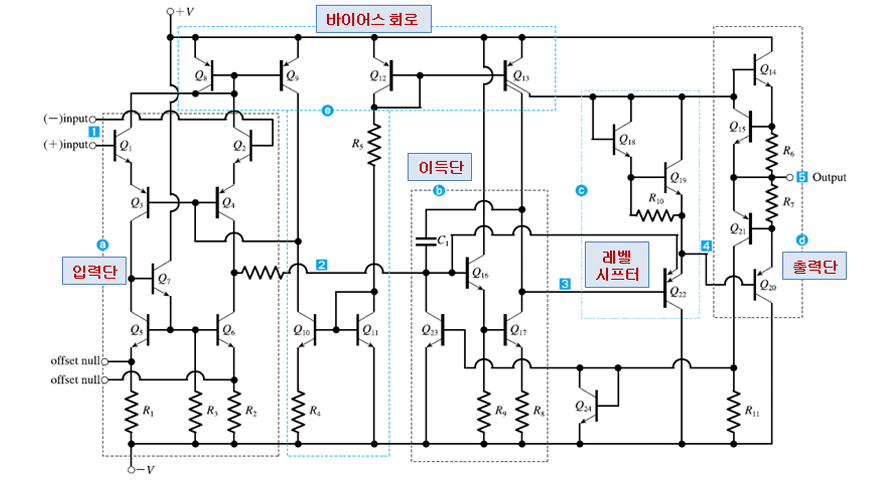

연산증폭기는 실로 엄청나게 복잡한 소자의 집합체입니다.

사진출처: 한양대학교 강의자료 일부 발췌

사진출처: 한양대학교 강의자료 일부 발췌

이러한 복잡한 회로의 구성에 의해

실제로 계산이 수행되는 것인데

그렇담 우리는 OP AMP를 배우기 위해서 위 회로를 전부다 해석할 수 있어야 되는거냐?

하면 그건 아닙니다.

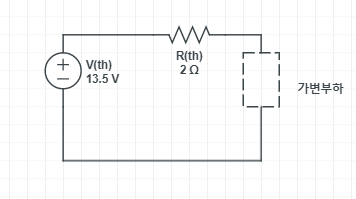

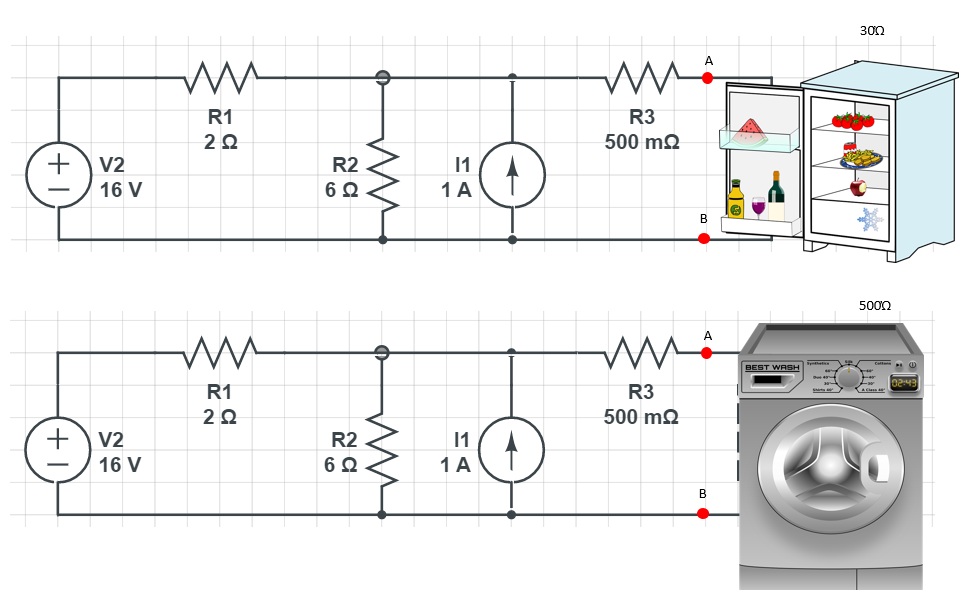

위 회로를 간단하게 나타낸 등가회로가 있습니다.

등가회로가 무엇인지는 앞에서 이미 설명한바 있죠..

일단 실제를 배우고 등가회로는 차차 설명드려보죠.

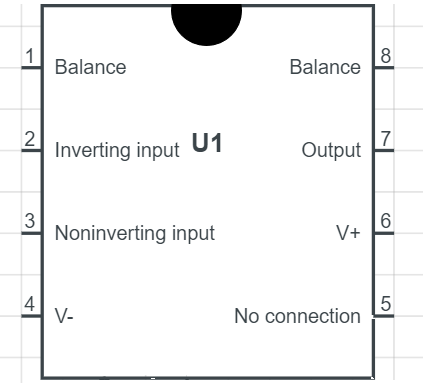

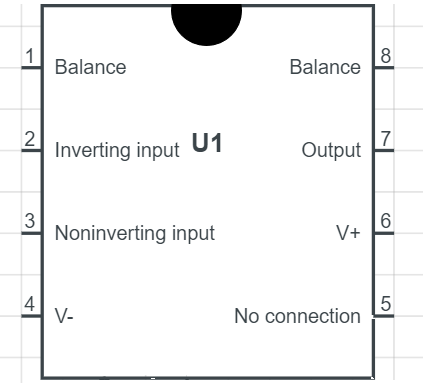

연산증폭기는 위와 같이 8개의 다릿발을 가지고 있습니다.

다릿발의 각각의 역할은 아래와 같습니다.

다릿발이 많아서 역할이 복잡해보이지만

실상 쓰이는 핀은 몇개 안됩니다.

일단 5번은 안씁니다.

1번과 8번은 이름에서도 유추할 수 있듯 영점을 잡는 거라고 생각하면 되는데.

쉽게 설명해보자면

Y=X 라는 수식을

수학적으로 해석하자면

X라는 입력에 100을 주면 출력으로 100이 나간다 정도로 이해하면 되겠지만

공학은 그렇지 않을 수 있거든요.

실제에는 X에 100을주면 Y가 99가 나오는 경우도 더러 있다는 겁니다.

실제는 이상적인 상황과는 다르게 여러 변수들이

상호작용하여

수학적으로 이해되지 않는 부분이 많다는 것이죠.

때문에 이런 값을 보정하기 위해서 1번과 8번핀을 쓰게되는데

자세한 원리는 여러분이 OP AMP를 사용하게 되는경우 메이커의 데이터시트를

찾아보시기 바랍니다.

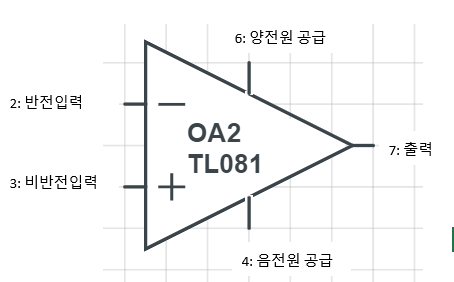

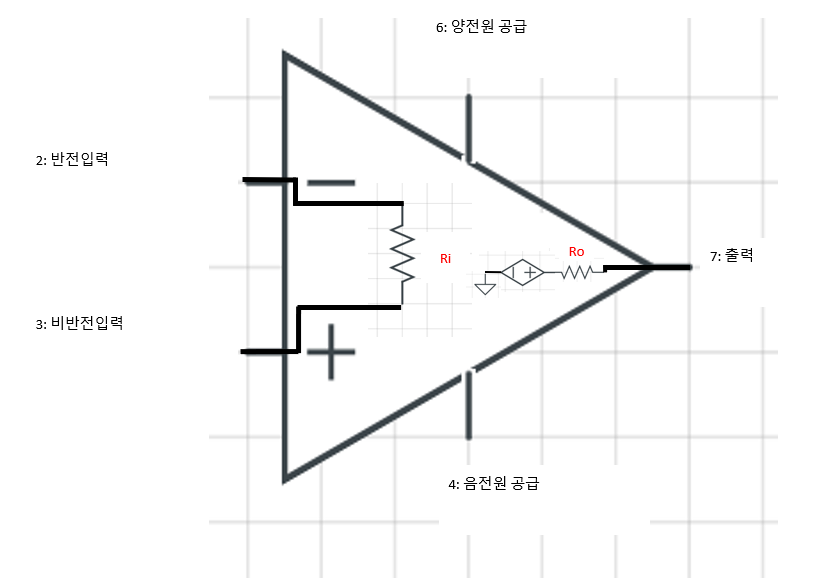

연산증폭기가 실제로는 이런 모습이지만

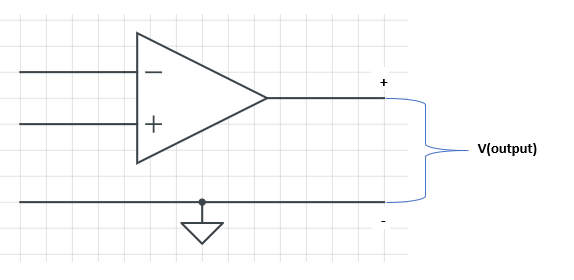

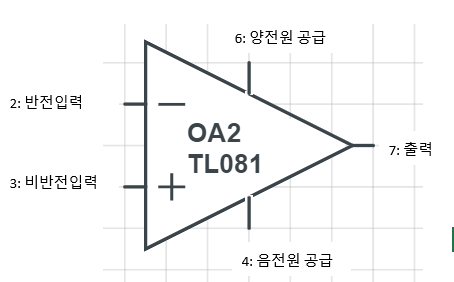

우리가 회로이론이라는 과목을 공부하게되면서 자주 접하는 그림은

아래그림일 겁니다

학부생이 배우는 회로이론은 이상적인 회로를 가정하고 배우기 때문에

영점 보정용핀은 통상 생략하고 표현이되며

구조를 보다시피 6번(양전원 공급)과 4번(음전원 공급)은 소자 자체를

구동시키기 위한 전원이라 생각하면 됩니다.

소자라함은

여러번 등장하는 위 사진 제품자체의 전원을 ON 시키기 위한 기능이죠.

별거 없어보이지만

아래에서 설명할 출력 전압의 최대치

기준이 되기 때문에 꽤나 중요한 의미를 지닙니다.

그래서 제목도 초록색으로 표시함.

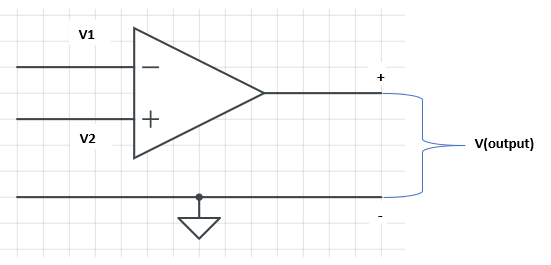

- 2번핀과 3번핀은 원하는 출력을 얻기 위해서 인가하는 입력핀

2번핀과 3번핀은 원하는 출력을 얻어내기 위해 집어넣는 입력으로써

4번핀 6번핀과는 그의미가 다릅니다.

4번과 6번핀은 소자를 ON 시키기 위해서 전원을 무작정 투입하는 과정이라면

2번과 3번핀은 출력을 원하는 만큼 얻기 위해서 세심하게 전원을 조작하는 느낌입니다.

수학을 예로들면 Y=2X라는 함수가 있는데

Y라는 출력을 4를 얻기위해서 X에 2를 입력해야되는 이치와 동일합니다.

여기에서 X에 2를 입력해야 된다는 것의 의미는

2번핀과 3번핀에 수학의 2에 해당하는 입력을 집어넣는다라고 이해하시면 되겠습니다.

7번핀은 2번핀과 3번핀의 결과물로서

위에 예로든 Y=2X에서 Y입니다.

다 좋은데... 그래서 대체 어떻게 수학적인 연산이 가능하다는 것인가?

학부생때 OP AMP를 달달 외우면서 스스로 던졌던 질문입니다.

앞으로 OP AMP 강좌를 여러강에 걸쳐 소개해드릴 겁니다.

위 질문에 대한 해답을 얻기 위해서는 OP AMP가 어떤식으로 동작되는지

그 원리를 정확히 이해해야 합니다.

때문에 지금 당장 답을 드릴 수는 없겠네요.

제가 써놓은 이문구.

다음 포스팅을 보더라도 까먹지 마시고 계속 상기하시면서 포스팅속에 해답을 찾아보세요.

사실 회로이론을 처음 접하면

너무 방대한 지식이 한꺼번에 주입되어

공부하는 목적자체를 잊고

큰틀을 보지 못하고 현재 배우고 있는거를 외우기 바쁜거 같습니다.

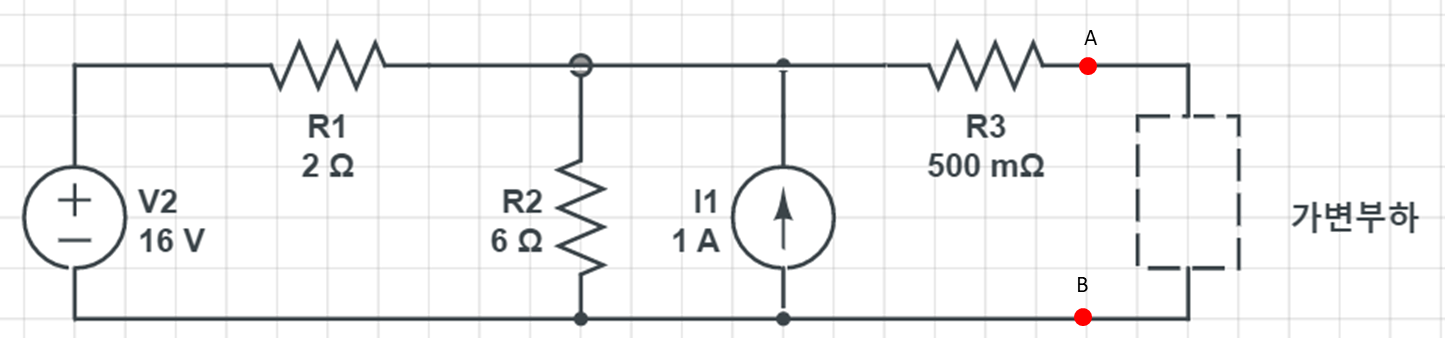

이 물음에 대한 해답을 위해서는

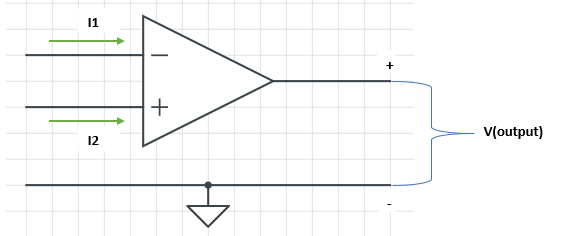

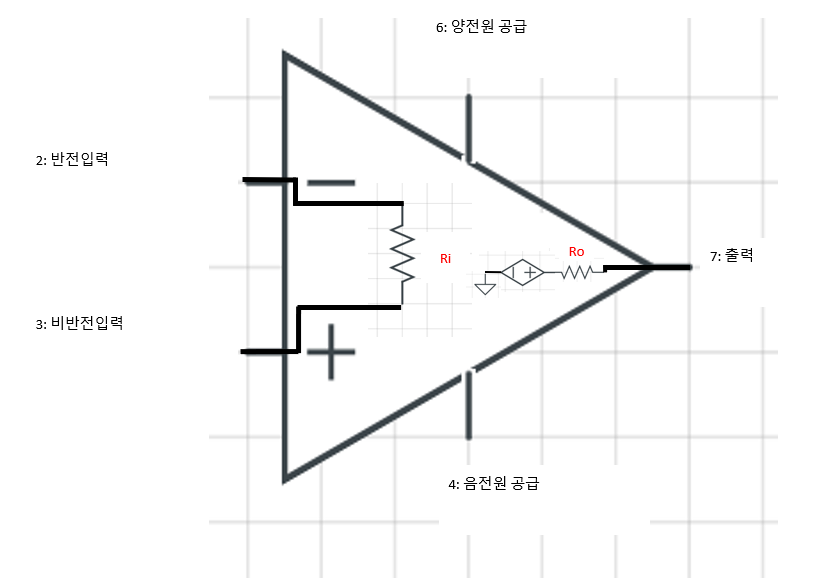

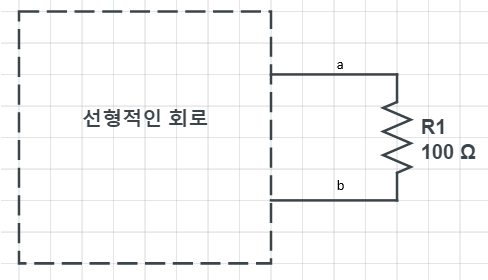

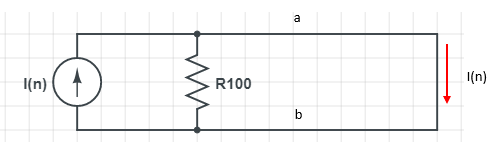

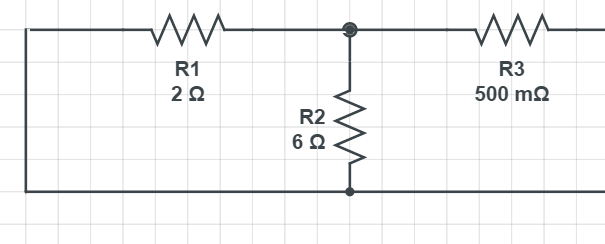

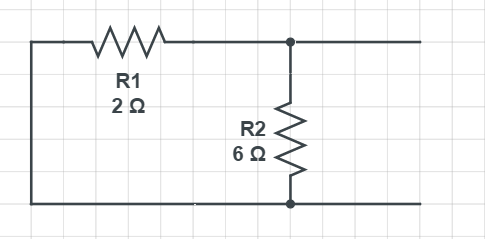

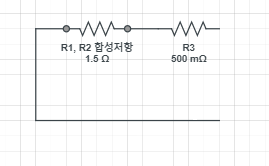

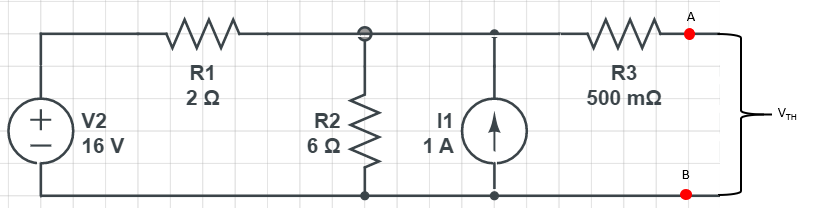

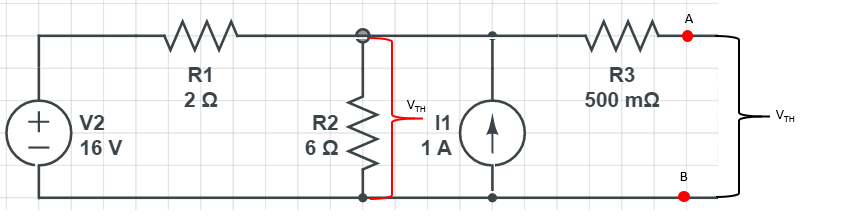

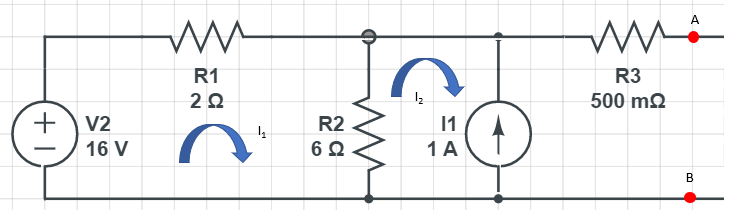

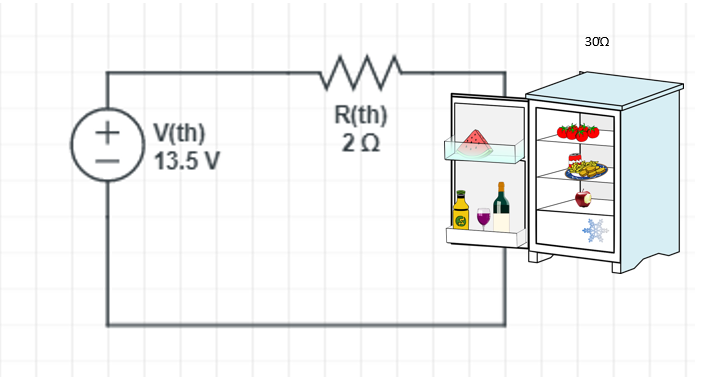

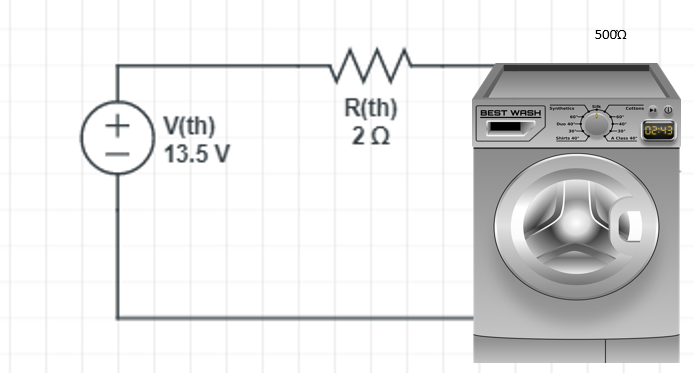

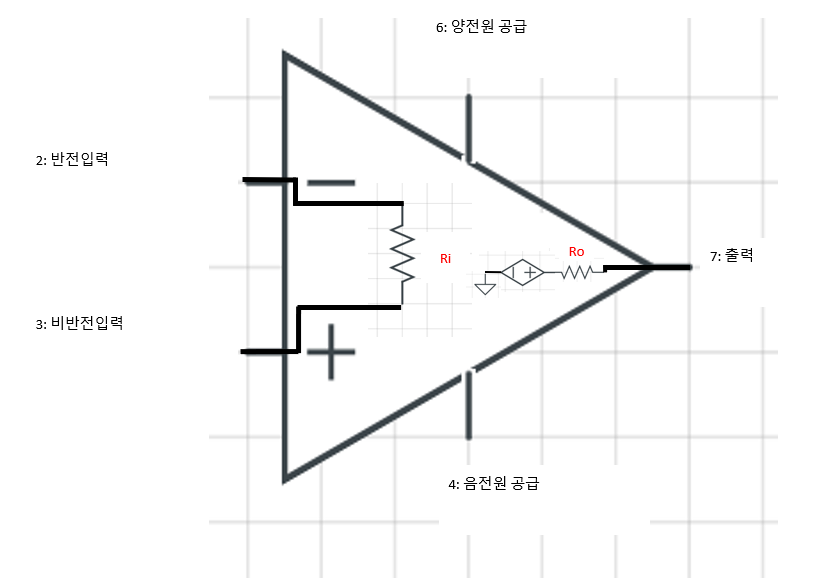

아래 그림을 이해하는 과정이 필요할 것 같습니다.

아래 그림은 허접하지만.

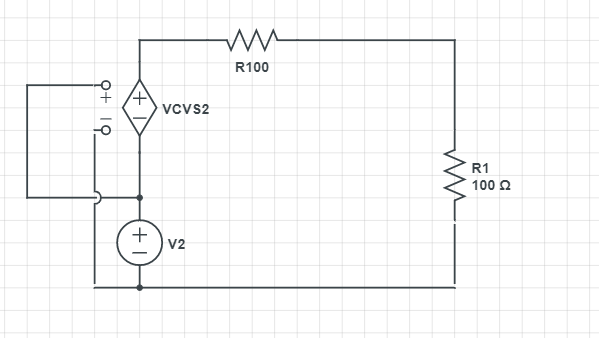

OP AMP의 내부회로를 테브난 등가회로로 대체한 그림입니다.

Ri 라는 것은 입력측의 테브난 등가저항을 나타내고

Ro는 출력측의 테브난 등가회로를 나타냅니다.

이제 설명드릴테니 잘 이해해보세요

2번핀과 3번핀을 멀티 테스터기로 전압을 찍었고 그값이 Vd가 나왔다고 칩시다.

출력쪽의 종속전원은 Vd에 A배 비례하는 전압을 내고 있는 구조인데

너무 간단하게도

Vd를 넣었는데 Vd에 A배가 출력되는 결과를 얻게 되었습니다.

실제로 Ri는 무한대에 가까운 아주아주 커다란 저항이고

Ro는 0옴과 가까운 아주아주 작은 저항입니다.

입력쪽에 인가된 전압은 실질적으로 개방회로와 같아서

손실이 없이 Vd가 그대로 입력되면

출력쪽의 저항 Ro는 그값이 매우작아서

마치 단락회로와도 같기때문에 전압강하 없이

Vd의 A배만큼 출력이 가능하다는게 이론적인 상식입니다.

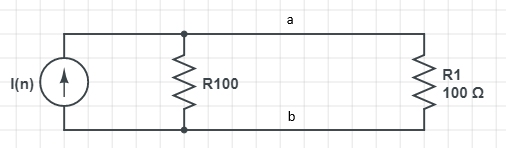

허나 진짜 그럴까요...?

입력 전압을 얼마나 넣건

출력이 내가 원하는 만큼 무한정 나올까요?

그런 소자는 세상에 존재하지 않는다가 정답이에요.

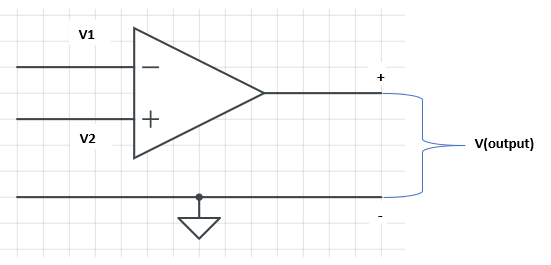

실제로는 입력핀에 인가한 전압

4번핀과 6번핀의 전압이 최대치라 보시면 됩니다.

정리하면 이렇습니다.

2번핀과 3번핀의 전위차를 Vd로 정의하고

7번핀과 접지간 전위차를 Vo로 정의하고

6번핀과 4번핀의 전위차를 Vcc로 정의하면

Vd * A(개루프이득) = Vo

-Vcc <= Vo <= Vcc

라는 것이죠.

결론은

Vd값이 아무리 크더라도 Vo는 Vcc에 종속된다는 것이 실제입니다.

보통 Vcc 전압으로는 DC 5[V] ~ DC 24[V]정도를 넣기 때문에

최대 출력전압이 +24[V] , -24[V] 에서 왔다리 갔다리 한다는 사실을 알 수 있죠.

오늘 배운 파트는

개방루프 형태를 배운건데요.

개방루프가 있다면 폐루프 형태 또한 존재하겠죠?

다음시간에 이어서 배워보도록 하겠습니다.